电感器广泛应用于各种电力电子线路中,在电源电路里更是不可或缺。像工业控制设备中的电磁继电器、电力系统的电功计量表(电度表)、开关电源设备输入和输出端的滤波器,以及电视接收与发射端的调谐器等,都离不开电感器。电感器在电子线路中的主要作用包括储能、滤波、扼流、谐振等。在电源电路中,由于处理的是大电流或高电压的能量传递,电感器多为 “功率型” 电感。与小信号处理电感不同,功率电感的设计因开关电源的拓扑方式不同而有不同要求,这也增加了设计的难度。当前电源电路中的电感器主要用于滤波、储能、能量传递以及功率因数校正等。电感器的设计涉及电磁理论、磁性材料以及安规等多方面知识,设计者需要清楚了解工作情况和相关参数要求(如电流、电压、频率、温升、材料特性等),才能做出合理的设计。

电感器可以根据应用环境、产品结构、形状、用途等分为不同种类。在开关电源中,根据用途的不同,电感器可分为以下几种:

- 共模滤波电感器(Common Mode Choke)

- 常模滤波电感器(Normal Mode Choke)

- 功率因数校正电感(Power Factor Correction - PFC Choke)

- 交链耦合电感器(Coupler Choke)

- 储能平波电感(Smooth Choke)

- 磁放大器线圈(MAG AMP Coil)

其中,共模滤波电感器要求两线圈具有相同的电感值、相同的阻抗等,因此采用对称性设计,其形状多为 TOROID、UU、ET 等。

共模滤波电感器又称共模扼流线圈(以下简称共模电感或 CM.M.Choke)或 Line Filter。在开关电源中,整流二极管、滤波电容以及电感中的电流或电压急剧变化会产生电磁干扰源(noise),同时输入电源中也存在工频以外的高次谐波噪声。这些干扰若不加以遏制,将对负载设备或开关电源本身造成损害。因此,各国安规机构对电磁干扰(EMI)发射量都作出了相应的管制规定。随着开关电源的开关频率日趋高频化,EMI 问题也日益严重,所以开关电源中必须设置 EMI 滤波器。EMI 滤波器需要对常模及共模噪声进行抑制,以达到规定标准。常模滤波器负责滤出输入或输出端两根线间的差模干扰信号,共模滤波器负责滤出两条入线的共模干扰信号。

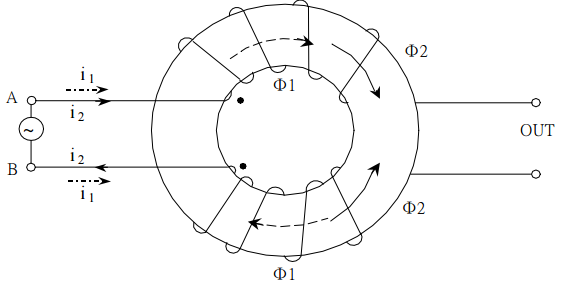

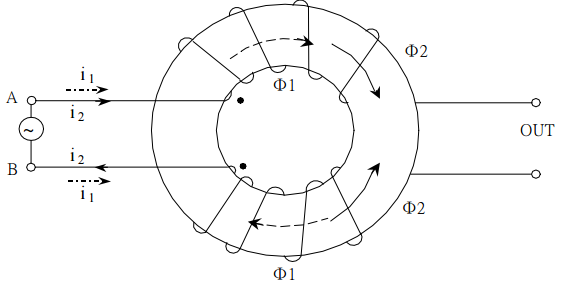

实际的共模电感根据工作环境的不同,可分为 AC CM.M.CHOKE、DC CM.M.CHOKE 和 SIGNAL CM.M.CHOKE 三种,在设计或选用时需要加以区分。但其工作原理是相同的,如图 1 所示:

在同一磁环上绕上两组方向相反的线圈,根据右手螺旋管定则,当在输入端 A、B 两端加上极性相反、信号幅值相同的差模电压时,会有实线所示的电流 i2,在磁芯中产生实线所示的磁通 Φ2。只要保证两绕组完全对称,磁芯中两不同方向的磁通就会相互抵消,总磁通为零,线圈电感几乎为零,对常模信号无阻抗作用。若在输入端 A、B 两端加上极性相同、幅值相等的共模信号时,会有虚线所示的电流 i1,在磁芯中产生虚线所示的磁通 Φ1,磁芯中磁通方向相同而互相加强,使每一线圈的电感值为单独存在时的两倍。由于 XL =ωL,因此这种绕法的线圈对共模干扰有很强的抑制作用。

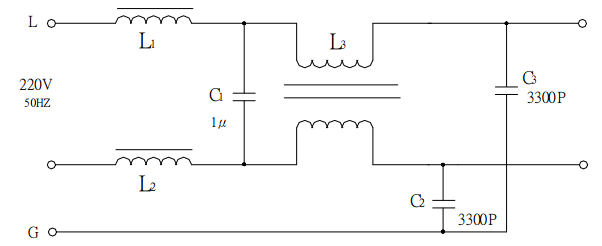

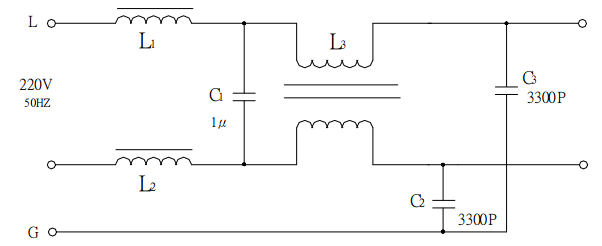

实际的 EMI 滤波器由 L、C 组合而成,设计时常常将差模与共模抑制电路组合在一起,如图 2 所示:

图中 L1、L2、C1 构成常模滤波器,L3、C2、C3 构成共模滤波器。设计时需要依据滤波电容的大小以及所需符合的安规标准来确定电感值。

在设计共模电感之前,需要考察线圈是否符合以下原则:

- 正常工作状态下,不致因通电电源电流而造成磁芯饱和。

- 对高频干扰信号要有足够大的阻抗,且有一定的频宽,而对工作频率的信号电流有的阻抗。

- 电感的温度系数应小,而分布电容宜小。

- 直流电阻应尽量小。

- 感应电感应尽量大,电感值需稳定。

- 绕组间的绝缘性须满足安规要求。

共模电感器的设计步骤如下:

- Step 0 SPEC 取得:确定 EMI 允许级别和应用位置。

- Step 1 电感值确定:

以图 3 所示的实际 EMI 滤波器电路为例:

已知 CX = 1.0 Uf,Cy = 3300PF,EMI 等级为 Fcc Class,Type 为 Ac Common Mode Choke。由电路图可知,共模信号由 L3 和 C2、C3 组成的共模滤波器抑制,实际 L3 与 C2 和 C3 构成两路 LC 串联电路,分别吸收 L 和 N 在线的噪声。只要确定滤波电路的截止频率,已知电容容量 C,就可以通过公式 fo= 1/(2π√LC),推导出 L → 1/(2πf o)2 C 来求出电感 L。

通常 EMI 测试频宽如下:

- 传导干扰:150KHZ →30MHZ(注:VDE 标准 10KHZ - 30M)

- 辐射干扰:30MHZ 1GHZ

实际的滤波器无法达到理想滤波器那样陡峭的阻抗曲线,通常可将截止频率设定在 50KHZ 左右。在此假设 f o = 50KHZ,则:

L =1/(2πfo)2 C = 1/ [( 23.1450000)2 330010?12 ] = 3.07mH

L1、L2、C1 组成(低通)常模滤波器,线间电容有 1.0uF,则常模电感为:

L = 1/ [( 23.1450000)2 110?? ] = 10.14uH

如此可得到理论要求的电感值。若想获得更低的截止频率 fo,则可进一步加大电感值,但截止频率一般不低于 10KHZ。理论上电感量越高对 EMI 抑制效果越好,但过高的电感将使截止频率更低,而实际的滤波器只能做到一定宽带,会使高频噪声的抑制效果变差(一般开关电源的噪声成分约为 5 ~10MHZ 间,但也有超过 10MHZ 的情形)。另外,电感量愈高,绕线匝数愈多,或 CORE 之 ui 越高,会造成低频阻抗增加(DCR 变大)。匝数增加使分布电容也随之增大,如图 4 所示,使高频电流全部经此电容流通。过高的 ui 使 CORE 极易饱和,同时制作也极困难,成本也较高。

3. Step 2 CORE 材质及 SIZE 确定:

从前述设计要求可知,共模电感器需不易饱和,需要选择低 B - H 角形比的材料。由于需要较高的电感值,磁芯的 ui 值也要高,同时还必须有较低的磁芯损耗和较高的 Bs 值。符合上述要求的 CORE 材质,目前以 Mn - Zn 铁氧体材料 CORE 为合适。

COEE SIZE 在设计时没有一定的规定,原则上只要符合所需电感量,且在允许的低频损耗范围内,使所设计的产品体积化即可。因此,CORE 材质及 SIZE 的选择应考虑成本、允许损耗、安装空间等因素。共模电感常用 CORE 之 ui 约在 2000 ~ 10000 之间。Iron Powder Core 也有低的铁损、高的 Bs 和较低的 B - H 角形比率,但其 ui 较低,一般不被应用于共模电感,而该类磁芯却是常模电感器的优选材料。

4. Step 3 确定匝数 N 和线径 dw:

首先确定 CORE 的规格,如本例采用 T18107、A10、AL = 8230±30%,则:

N = √L / AL = √(3.0710? ) / (823070%) = 23 TS

线径以电流密度 3 ~ 5A /mm2 为选择原则,若空间允许可选择尽量低的电流密度。假设本例输入电流 I i = 1.2A,取 J = 4 A /mm2,则:

Aw = 1.2 / 4 = 0.3 mm2 ,对应的线径为 Φ0.70 mm

实际的共模电感还需要通过实做样品进行测试,才能确认设计的可靠性。因为制作工艺的差异会导致电感参数的差异,从而影响滤波效果。例如,分布电容的增加会使高频噪声更易传递,两绕组的不对称性会使两组感量差异变大,对常模信号形成一定阻抗。

- 共模电感器的作用是滤除线路中的共模噪声,设计时要求两绕组具有完全对称的结构,电参数相同。

- 共模电感的分布电容对抑制高频噪声有负面影响,应尽量减小。

- 共模电感的感值与须滤除的噪声频带及配合电容容量有关,通常感值在 2mH ~50 mH 之间。