I2C 总线加上拉电阻的必要性

出处:网络整理 发布于:2025-08-25 16:42:09

I2C 总线的基本结构

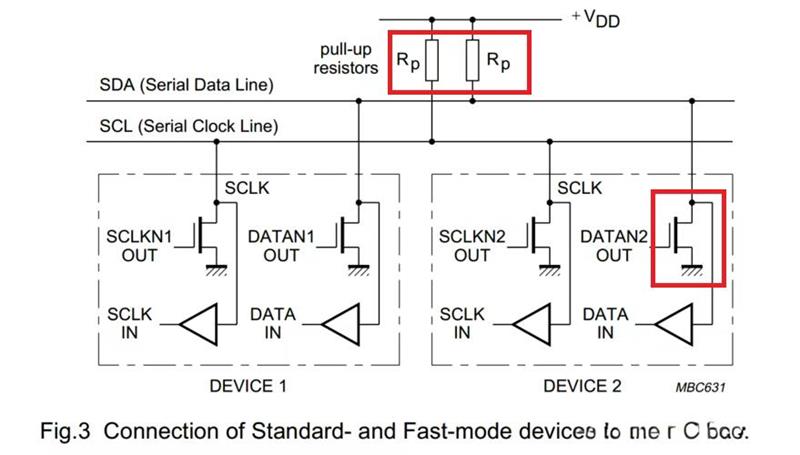

图 1 I2C 总线结构图

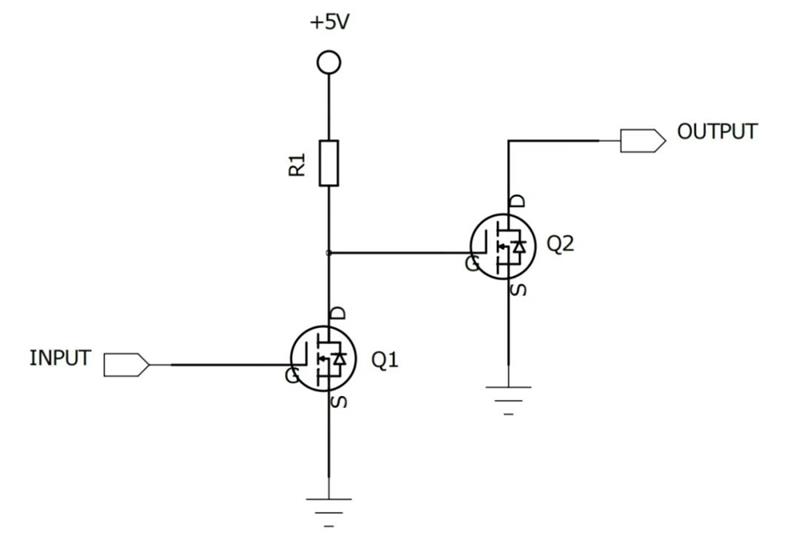

OD 门电路的工作原理

图 2 典型的 OD 门电路

上拉电阻的作用

图 3 I2C 总线的线与逻辑

上拉电阻的选择

版权与免责声明

凡本网注明“出处:老太阳集团tcy8722网站电子市场网”的所有作品,版权均属于老太阳集团tcy8722网站电子市场网,转载请必须注明老太阳集团tcy8722网站电子市场网,,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 简述计算机总线的分类2025/9/4 17:12:23

- 深度剖析三进线两母联供电系统设计方案2025/9/3 10:37:39

- 汇流排是什么汇流排好还是线接好2025/8/28 17:13:00

- 安森美 USB - C 电池充电器解决方案2025/8/28 15:45:10

- 深入解析安世半导体 NEX53100 - Q100:双口 PD3.2 快充协议控制器的卓越性能2025/8/22 16:57:23