在半导体封装等电子领域,连接工艺的可靠性和性能至关重要。共晶焊接工艺作为一种先进的连接技术,凭借其独特的优势,在电子封装领域得到了广泛应用。接下来,我们将深入探讨共晶焊接工艺的基本原理、特点、应用场景以及在实际操作中需要注意的问题。

在深入探讨共晶焊接工艺前,我们先来了解其基本原理。当两种组元在液态可完全互溶、固态仅有限互溶且存在共晶转变时,所构成的二元合金相图即为共晶相图。像 Pb - Sn、Pb - Sb、Cu - Ag、Al - Si 等合金的相图都属于这一类型。以典型的二元共晶相图 ――Pb - Sn 合金相图为例,其中水平线 CED 被称为共晶线。在该水平线对应的温度(183℃)下,成分为 E 点的液相会同时结晶出成分为 C 点的 α 固溶体和 D 点的 β 固溶体,即 L→(α_C + β_D)。这种在特定温度下,由特定成分的液相同时生成两种成分与结构均不同的新固相的转变过程,称为共晶转变或共晶反应。共晶反应的产物是两相构成的机械混合物,称为共晶体或共晶组织。发生共晶反应的温度称为共晶温度,代表共晶温度与共晶成分的点称为共晶点,具有共晶成分的合金则称为共晶合金。在共晶线上,成分位于共晶点左侧的合金为亚共晶合金,位于右侧的则为过共晶合金。所有具有共晶线成分的合金液体,冷却至共晶温度时都会发生共晶反应。在共晶反应过程中,L、α、β 三相平衡共存,它们的成分保持固定,但各自的重量会不断变化。

以 Pb - Sn 合金相图为例,当合金液体冷却至共晶点 E 时,液体同时被 Pb 和 Sn 饱和,进而发生共晶反应:L→(α_C + β_D),析出成分为 C 的 α 相和成分为 D 的 β 相。反应结束后,得到 α + β 的共晶组织。由于从成分均匀的液相中同时结晶出两种成分差异显著的固相,必然伴随元素的扩散过程。假设先析出富铅的 α 相晶核,随着其生长,周围液体将因铅元素减少而锡元素富集,这为 β 相的形核创造了条件;而 β 相的生长又会反过来促进 α 相的进一步形核。如此一来,两相交替形核、相互促进,使得共晶组织通常较为细密,呈现片状、针状、棒状或点球状等形态。总体而言,共晶组织具有结构稳定、机械性能优良的特点,能够在异种金属间形成稳固的连接。

共晶焊接的具体方式是:利用芯片背面的金硅合金,与基座或引线框架上镀层(如银层)在高温氨气氛保护下(温度范围 400~440℃)发生反应形成合金,从而实现芯片的固定。这种工艺要求芯片背面预先蒸镀金层,其导电与导热性能优异,适用于尺寸较小的芯片,尤其适合功率晶体管芯片。与采用合金焊料的装片方式相比,这种方式更有利于芯片工作时的散热。

共晶焊接技术在电子封装领域应用广泛,涵盖芯片与引线框架或基板的连接、基板与管壳的装配、管壳封帽等场景。与传统的环氧导电胶连接相比,共晶焊接具有热导率高、电阻小、传热迅速、可靠性强、连接后剪切力大等优势,适用于高频、大功率器件中芯片与基板、基板与管壳的互联。对于有较高散热需求的功率器件,采用共晶焊接能有效提升散热效率。

共晶焊接借助共晶合金的特性完成焊接过程,共晶合金具有以下显著特点:

- 熔点低于纯金属组元:相较于熔化焊工艺,大幅简化了操作流程。这使得在焊接过程中,不需要过高的温度来熔化焊接材料,降低了对焊接设备和工艺的要求。

- 流动性优于纯金属组元:凝固过程中可避免枝晶对液体流动的阻碍,铸造性能更优。良好的流动性使得共晶合金能够更好地填充焊接部位的缝隙,保证焊接的质量。

- 恒温转变(无凝固温度范围):减少了偏聚、缩孔等缺陷。这意味着在焊接过程中,共晶合金能够更加均匀地凝固,避免了因温度不均匀而产生的缺陷,提高了焊接的可靠性。

- 共晶凝固能形成多种显微组织:尤其是规则排列的层状或杆状共晶组织,可成为性能优异的原生复合材料。这些特殊的显微组织赋予了共晶合金良好的机械性能和物理性能。

共晶现象指共晶焊料在较低温度下发生共晶成分的熔合,此时共晶合金直接从固态转变为液态,不经过塑性阶段,其熔化温度被称为共晶温度。“真空 / 可控气氛自动共晶炉” 是近年来国际上推出的新型设备,可实现各类器件的共晶工艺。该设备在共晶过程中无需使用助焊剂,且具备抽真空或充惰性气体的功能 ―― 在真空环境下进行共晶能有效减少空洞,若配合专用夹具,还可实现多芯片的共晶操作。

真空 / 可控气氛自动共晶炉主要用于芯片焊接,其中芯片与基板的焊接是其应用方向。通常采用金锡(AuSn 80/20)、金硅(AuSi)、金锗(AuGe)等合金焊片,将芯片焊接至基板(载板)上。具体操作时,需将合金焊片置于芯片与基板间的焊盘位置。为防止氧化物生成,芯片背面通常会镀一层金。上述三种合金焊料已在半导体器件中成功应用,具备优良的机械性能与热传导性。

在微波、毫米波电路中,常用的合金焊料为 AuSn(熔点 280℃)和 AuGe(熔点 365℃)。由于两者熔点差异较大,实际应用中一般先用 AuGe 合金将膜电路焊接在载板上,再用 AuSn 合金焊接微波芯片、电容等元器件。为避免芯片等元器件受到高温热冲击,部分企业采用 AuSn 合金将薄膜电路共晶焊接到载板,而其他芯片元器件则采用导电胶焊接。

在多芯片组件中,焊接芯片与基板所用的材料及组装工艺,与混合电路中的应用大致相同。和混合电路类似,90% 以上的多芯片组件会使用低成本且易于返修的环氧树脂;焊料或共晶焊接法则主要用于大功率封装的内部互联,或需满足宇航级要求的封装互联。多芯片组件作为当前微组装技术的典型产物,是一种能满足民用、军用、宇航电子装备及巨型计算机在微小型化、高可靠性、高性能等方面迫切需求的先进微电子组件。它将多个芯片及其他片式元器件集成在一块高密度多层互连基板上,并封装于管壳内。凭借高密度、高性能、高可靠性、轻重量、小体积等显著优势,多芯片组件被广泛应用于航空航天、军用通信、常规武器等军事领域。目前,多芯片组件在密度持续提升的同时,正朝着大功率、高频方向发展,而多芯片共晶内互联工艺是推动大功率、高频器件制造水平提升的关键技术。

使用真空 / 可控气氛自动共晶炉进行芯片共晶焊接时,需要重点关注以下几个方面的问题:

- 焊料的选择:焊料是共晶焊接的要素,可作为焊料的合金种类多样,如 AuGe、AuSn、AuSi、SnIn、SnAg、SnBi 等,每种焊料因自身特性适用于不同场景。例如,含银的 SnAg 焊料易与镀银端面结合,含金、铟的合金焊料则易与镀金端面接合。根据被焊件的热容量,共晶炉的焊接温度通常需设定为高于焊料合金共晶温度 30~50℃。此外,芯片的耐温能力与焊料共晶温度的匹配也是关键 ―― 若焊料共晶温度过高,可能改变芯片材料的物理化学性质,导致芯片失效。因此,选择焊料时需综合考虑镀层成分与被焊件的耐受温度。另外,焊料存放时间过长会导致表面氧化层过厚,由于焊接过程无人工干预,氧化层难以去除,熔化后残留的氧化膜会造成焊接空洞。虽然焊接时向炉腔充入少量氢气可还原部分氧化物,但使用新焊料以将氧化程度降至。

- 温度控制工艺曲线参数的设定:共晶焊接技术主要应用于高频电路、大功率电路以及需满足宇航级标准的电路。焊接过程中的热量流失、热应力、环境湿度、颗粒杂质及冲击振动等,是影响焊接质量的关键因素。其中,热损伤会导致薄膜器件性能下降;湿度过高可能引发部件黏连、磨损及异常附着;散热部件功能失效则会阻碍热量传导。

共晶焊接中常见的问题是加热基座温度低于共晶温度,此时焊料虽能熔化,但不足以促使芯片背面镀金层扩散,操作者易误将焊料熔化当作共晶完成;反之,加热基座持续工作时间过长会造成电路金属层损坏。因此,共晶过程中温度与时间的精准控制至关重要。

由于共晶所需温度较高(尤其是采用 AuGe 焊料时),对基板及薄膜电路的耐高温性能提出了明确要求 ―― 需耐受 400℃高温,且在此温度下电阻与导电性能不受影响。值得注意的是,共晶温度控制并非简单达到某一固定值,而是要经历完整的温度曲线变化过程。在此过程中,设备需具备处理抽真空、充气、排气等随机事件的能力,这也是共晶炉的功能之一。

多芯片共晶的温度控制与单芯片存在显著差异。因芯片材料、共晶焊料不同,其共晶温度往往存在差异,此时需采用阶梯式共晶工艺:先处理共晶温度较高的焊料,再处理温度较低的焊料。共晶炉控制系统可预设多条温度曲线,每条曲线可设置 9 个阶段,通过链接扩展后多可达 81 个阶段,且在曲线运行中可穿插充气、抽真空、排气等工艺步骤。

3. 降低空洞率:共晶完成后,空洞率是一项检测参数,如何有效降低空洞率是共晶工艺的关键技术环节。空洞的形成通常与焊料表面氧化层、微小杂质颗粒、熔化时未排出的气泡有关。氧化层会阻碍金属表面结合物的相互渗透,其残留缝隙在冷却凝固后形成空洞;杂质与气泡也会直接导致空洞产生。

共晶焊接产生的空洞会降低器件可靠性,增加芯片断裂风险,同时导致器件工作温度升高、管芯粘贴强度下降,进而影响焊接效果及整体电气性能。降低空洞率的主要措施包括:

- 共晶前彻底清洁器件与焊料表面,清除各类杂质。

- 共晶过程中在器件上方设置加压装置,直接施加正向压力。

- 在真空环境下执行共晶操作。

- 实现多芯片共晶:在多芯片组件的共晶过程中,随着芯片尺寸不断缩小、数量持续增加,必须采用专用工装夹具辅助完成。这类夹具不仅要能固定芯片与焊料的位置,还需具备操作便捷、耐受高温环境且形态稳定的特性。由于部分芯片尺寸仅 0.5mm2 甚至更小,人工定位难度大,操作不便,因此共晶炉通常适用于焊接 1mm2 以上的芯片。共晶过程中,气流变化可能导致芯片移位,故借助夹具定位是必要环节。

夹具除需满足加工精度要求外,还需能在高温下保持形态稳定,其物理化学性质不会因高温发生改变,或其变化不会对共晶过程产生不利影响,甚至能辅助提升共晶效果。同时,夹具材料需易于加工,否则会阻碍功能实现,且操作便利性也是重要考量因素。高纯石墨基本符合上述要求,因此共晶炉夹具多选用此类材料,其特点包括:

- 高温下变形量小,对器件影响轻微。

- 导热性能优异,利于热量传递,能保证温度均匀性。

- 化学稳定性强,长期使用不易变质。

- 可塑性好,便于加工成型。在氧化环境中,石墨中的碳会生成 CO 和 CO?,具有干燥氧气的作用。此外,石墨属于各向同性材料,晶粒在各方向分布均匀密集,受热时温度均匀,焊接元器件固定于石墨上时,热量可直接传导,确保加热均匀、焊接面平整。

- 基板与管壳的焊接:与芯片和基板的焊接流程相类似,基板与管壳的焊接也是共晶焊接的重要应用领域。因基板通常尺寸大于芯片,且材质更厚更坚硬,对定位精度要求较低,共晶炉能更高效地完成这类焊接操作。

- 封帽工艺:器件封帽是共晶炉的另一项应用。器件外壳多采用陶瓷等基材,外部镀金镍层制成。“陶瓷封装” 在实际应用中因装配便捷、内部连接易于实现且成本较低,成为优选封装方案。陶瓷材质能抵御恶劣外部环境,如高温、机械冲击与振动,且硬度高,热膨胀系数接近硅材料。这类器件的封装可采用共晶焊接方式:陶瓷腔体上部设有密封环,用于与盖板进行共晶焊接,以实现气密或真空封焊。通常金层厚度需达到 1.5μm,但由于工艺处理及高温烘烤的需求,腔体与密封环需电镀 2.5μm 的金层,多余的金层可防止镍迁移。镀金盖板可作为陶瓷管壳的气密性封焊材料,共晶前通常需进行真空烘烤处理。此外,共晶炉还可应用于芯片电镀凸点再流成球、共晶凸点焊接、光纤封装等工艺环节。

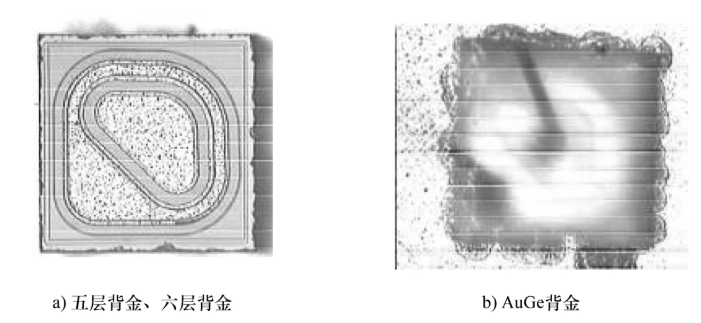

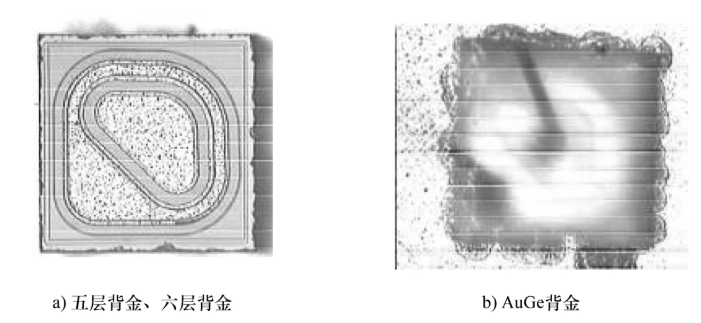

芯片背面采用不同合金材料时,在装片过程中其周边会出现不同的合金溢出情况。其中,采用五层背金或六层背金的芯片,其周边未出现合金溢出的痕迹;而采用 AuGe 背金的芯片,周边则有明显的合金溢出迹象,不同合金背金的溢出表现存在显著差异。

共晶焊接装片工艺同样存在一定的局限性。由于共晶装片需要依靠机械手施加向下的压力才能形成良好的共晶结构,若装片机械手上的吸嘴截面与芯片不平行,会导致芯片受力不均,进而出现芯片一侧与银形成牢固的共晶合金连接,而另一侧连接不牢固的现象。同时,加压时间与压力大小均有明确规定值。相关研究针对芯片表面材料的极限应力表明,当压强在 50MPa 以内时,芯片处于安全状态(硅的临界压强值为 53.6MPa)。

共晶焊接工艺作为一种先进的连接技术,在电子封装领域具有重要的应用价值。通过深入了解共晶焊接工艺的基本原理、特点、应用场景以及在实际操作中需要注意的问题,我们可以更好地发挥共晶焊接工艺的优势,提高电子封装的质量和可靠性。同时,我们也应该认识到共晶焊接装片工艺存在的局限性,不断探索和改进工艺,以满足日益增长的电子封装需求。