在当今半导体制造领域,2.5D/3D 封装技术作为前沿的先进封装工艺,实现方案丰富多样。它涵盖了芯片减薄、芯片键合、引线键合、倒装键合、TSV、塑封、基板、引线框架、载带、晶圆级薄膜工艺等多种类型,并且会根据不同应用需求和技术发展动态调整。部分工艺需针对 2.5D/3D 封装的特定要求进一步发展,例如 3D 封装中的引线键合技术,对线弧高度、焊点尺寸等有了更高标准,需要工艺上的改良与创新。在众多相关技术中,TSV 技术因其独特的优势,成为实现多功能、高性能、高可靠性,以及更轻、更薄、更小的系统级封装的有效手段之一,也被称为第四代封装技术。

与传统的引线键合相比,TSV 能大幅缩短互连线长度,降低信号传输延迟与损耗,提升信号传输速度与带宽,同时减少功耗并缩小封装体积。作为 2.5D/3D 封装的技术,TSV 与其他采用基板、薄膜布线等中介的 3D 封装不同,芯片间通过导电通孔与焊料键合连接,热失配程度小,互连长度更短。

TSV 技术的发展历程颇为漫长。20 世纪 80 年代中期,垂直 TSV 中填充导体的概念已被明确提出,但当时尚未实现。20 世纪 90 年代中期,博世公司研发出深反应离子刻蚀 (DRIE) 技术,使得在硅晶圆上刻蚀出垂直深孔成为可能。20 世纪末,成功实现了用钨或多晶硅导体填充的高深径比 TSV。进入 2000 年以后,深孔内电镀铜逐渐成为填充高深径比 TSV 的主要方式。此后,晶圆键合、凸点制造、晶圆薄化及化学机械抛光等技术的进步,进一步推动了 TSV 封装技术的完善。

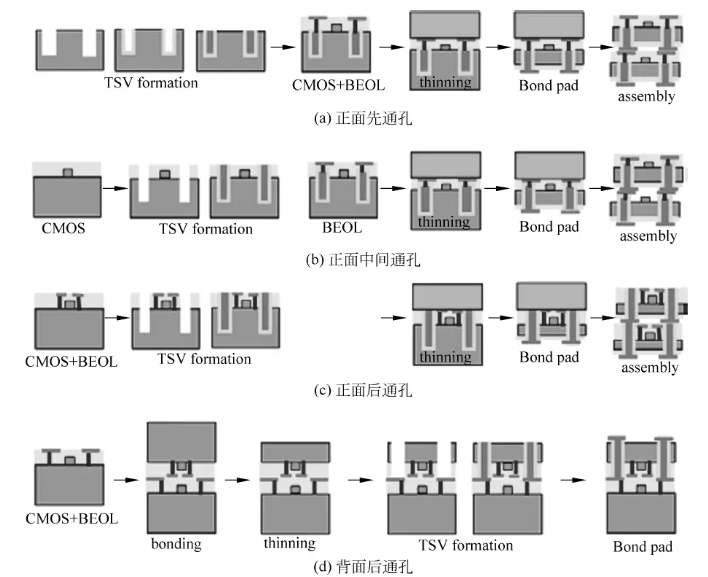

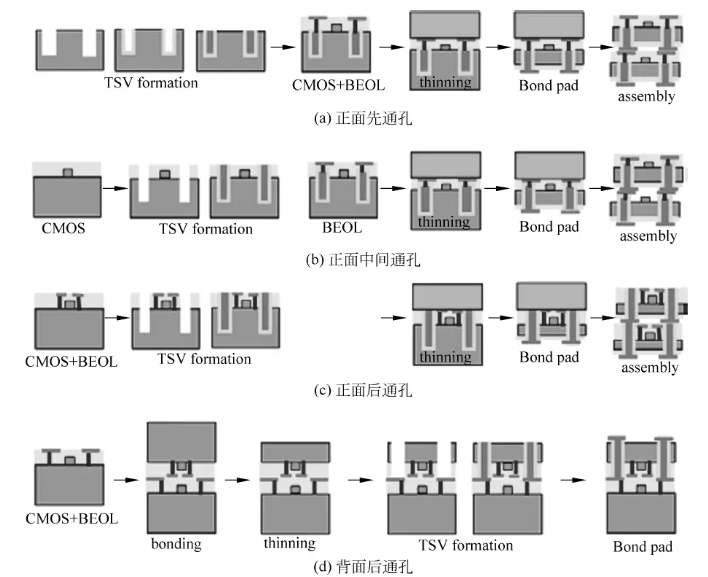

TSV 技术本质上属于晶圆级制程,其制作可融入集成电路制造工艺的不同环节,具体可分为正面先通孔、正面中间通孔、正面后通孔及背面后通孔四种类型。

- 正面先通孔:在初始硅衬底上先形成通孔,即在芯片前道制造工艺的有源层形成之前就完成通孔制作,此时 TSV 制作可在晶圆制造厂前端金属互连工序前进行。

- 正面后通孔:在芯片后道工艺完成后再制作通孔。该方案的显著优势是无需改变现有集成电路的流程与设计,同时还能降低种子层沉积成本、缩短电镀时间并提高产能,目前已有部分厂商在高端 Flash 和 DRAM 领域采用这一技术。

- 正面中间通孔:当 TSV 孔在 CMOS 与芯片后段制程 (Back End of Line,BEOL) 之间制作时,称为正面中间通孔,其中 BEOL 指芯片制造的后段工序,始于单个器件完成后的层金属互连,在晶圆制造厂内完成。

- 背面后通孔:在芯片或晶圆与另一晶圆键合后,再在背面钻孔。

TSV 制作的工艺流程具体如下:

- 在硅片上钻制深孔,深度超过 TSV 的目标厚度。

- 沉积介质层。

- 在硅片表面及深孔内沉积阻挡层、黏附层与种子金属层。

- 通过电镀铜或采用其他导电材料填充深孔。

- 利用化学机械抛光实现表面平坦化,并去除多余的种子金属层。

- 通过磨削或刻蚀使铜层或通孔导电层暴露出来。

TSV 工艺对晶圆厚度要求严格,需控制在 75μm 以内。随着 TSV 封装密度提升与孔径缩小,晶圆厚度还在不断减小。传统封装的减薄工艺通常只需将晶圆减至 200 - 350μm,特殊封装也仅需减至 150 - 180μm,此时硅片仍有足够厚度承受减薄过程中磨削造成的损伤与内在应力,且自身刚性便于搬送。但 TSV 工艺要求晶圆减薄至 50μm 以下,如何减少减薄损伤、实现柔性晶圆的稳定搬送成为新的挑战。

传统减薄工艺中,粗磨与精磨后残留的表面损伤是导致硅片破碎的主要原因。磨削属于物理损伤性工艺,通过物理施压、损伤、破裂与移除过程去除硅材料。为消除这类表面损伤与应力,行业尝试了干法抛光、湿法抛光、干法刻蚀、湿法刻蚀等多种方法。目前业界的主流解决方案是采用一体化设备,将硅片的磨削、抛光、保护膜去除及划片膜粘贴等工序整合在同一设备中,通过机械式搬送系统使硅片从磨削到粘贴划片膜的全过程都被吸附在真空吸盘上,始终保持平整状态。当硅片粘贴到划片膜上后,即使厚度薄于划片膜,也会顺应膜的形状保持平整,不再发生翘曲或下垂,从而解决了搬送难题。

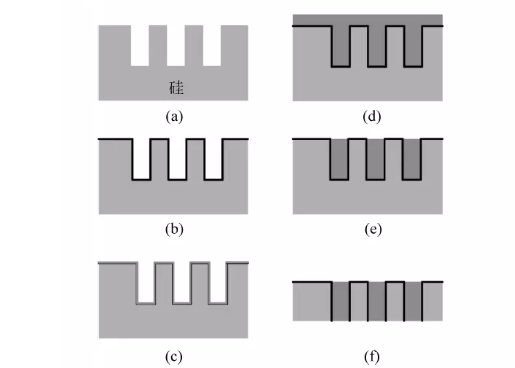

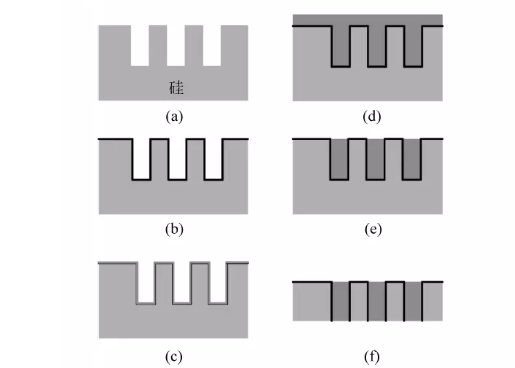

- 钻孔:晶圆钻孔是 TSV 工艺的环节,目前主要采用干法刻蚀 (又称 Bosch 刻蚀) 与激光刻蚀两种方式。Bosch 刻蚀工艺初为 MEMS 技术开发,其特点是快速交替进行硅去除 (采用 SF?等离子刻蚀) 与侧壁钝化 (采用 CF?等离子沉积) 过程。干法刻蚀速率可达 50μm/min,深宽比能达到 1:80,精度为亚微米级。激光刻蚀无需掩膜,省去了光刻胶涂敷、曝光、显影及去胶等工序。韩国三星公司已将该技术应用于存储器堆叠中。激光刻蚀的深宽比约为 7:1,性能弱于干法刻蚀,更适合芯片上通孔数量较少的场景;若通孔数量超过 10000 个,采用光刻结合干法刻蚀的效率更高。此外,当通孔尺寸缩小至 10μm 以下时,激光钻孔能否进一步缩小孔径仍面临挑战。

- 通孔绝缘:通孔绝缘通常通过 CVD 工艺沉积氧化物 (SiO?) 绝缘层,原料多采用硅烷或 TEOS。若在芯片电路制造完成后进行 TSV 绝缘与填充,为避免影响已完成的电路部分,需选择适宜的沉积温度。TEOS 沉积的典型温度为 275 - 350℃,可获得性能合适的功能性绝缘层;而对于 CMOS 图像传感器、存储器等应用,则要求更低的沉积温度。目前,部分设备制造商已开发出低温氧化物沉积技术,可在室温下沉积薄膜作为 TSV 的高效有机绝缘层。

- 阻挡层、种子层与填镀:在铜通孔工艺中,通常采用溅射方式沉积 TiN 黏附 / 阻挡层与铜种子层。但对于深宽比大于 4:1 的通孔,传统 PVD 直流磁控技术的台阶覆盖效果欠佳,而基于离子化金属等离子体 (IMP) 的 PVD 技术可实现孔侧壁与底部铜种子层的均匀沉积。由于电镀铜成本较低,种子层沉积后通常采用电镀铜填充通孔。不过,TSV 电镀时,孔口因效应会聚集更多电力线,导致此处电流密度远高于孔内;若不使用添加剂,孔口沉积速率会远快于孔内,加之孔内铜离子交换困难,容易出现孔口填满而孔内未完全沉积的情况。因此,需通过添加剂调节孔底部、侧壁与表面的电镀沉积速率 (抑制孔口沉积、增强底部沉积),或采用周期反向脉冲电流电镀,以实现通孔的完整填充。无空洞镀铜填充耗时较长,会降低生产效率,这是 TSV 镀铜填充面临的问题。

TSV 键合所采用的工艺包括金属间键合技术与高分子黏结键合等。键合的目标是让芯片或元件之间形成稳定的机械连接、电连接和热传导通道,将原本分立的芯片与元件整合为一个完整的封装产品。

从键合过程的特点来看,金属间键合主要分为热压键合和共晶键合两类。例如,铜 - 铜键合采用热压键合方式,而铜锡、金锡等键合则属于共晶键合。铜 - 铜热压键合的原理是:在真空环境或保护性气氛中,对紧密贴合的两个铜表面施加高温和高压,并保持足够长的时间,使两个键合面的铜原子充分扩散,终融合为一个整体,从而实现键合。不过,这种键合方式耗时较长,对工艺条件的要求也更为严苛。

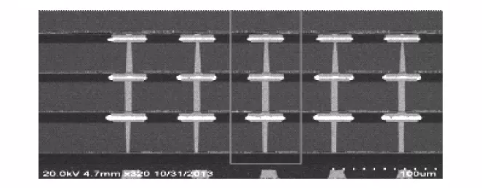

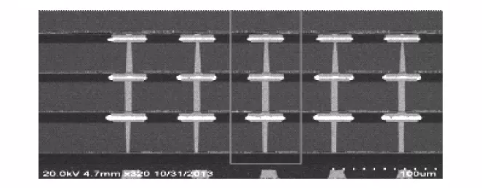

近年来,低温金属键合成为封装领域的研究热点。研究人员希望找到一种能在较低温度下形成良好电连接和机械结合,且反应产物可耐受高温的键合方式。铜 - 锡键合因其优异的电学和热学性能,以及较低的键合温度 (锡的熔点为 232℃) 而成为。铜 - 锡共晶键合过程中,低温下金属锡熔化形成液态,促使铜与锡充分接触,加速两者相互扩散,快速生成亚稳态高熔点金属间化合物 Cu?Sn?(熔点 415℃) 和稳态化合物 Cu?Sn (熔点 676℃),进而完成键合。这种键合方式在多层堆叠时,能有效避免已键合部位因后续键合过程中的热量而熔化,对三维封装的可靠性至关重要。此外,由于锡焊料具有良好的形变能力,铜 - 锡键合对键合表面的平整度和洁净度要求不高,即便表面存在一定起伏或微小颗粒,也能形成良好的键合。同时,液态锡能加快铜与锡的扩散速度,使键合效率更高。随着互连密度的提升,发展的混合键合技术也可能成为重要选择。

借助 TSV 技术可实现 2.5D 和 3D 封装,这类封装在当前 3D 封装方案中,在封装密度和互连长度方面均具有明显优势。因此,TSV 的应用进展在一定程度上反映了 3D 封装领域的前沿发展态势。

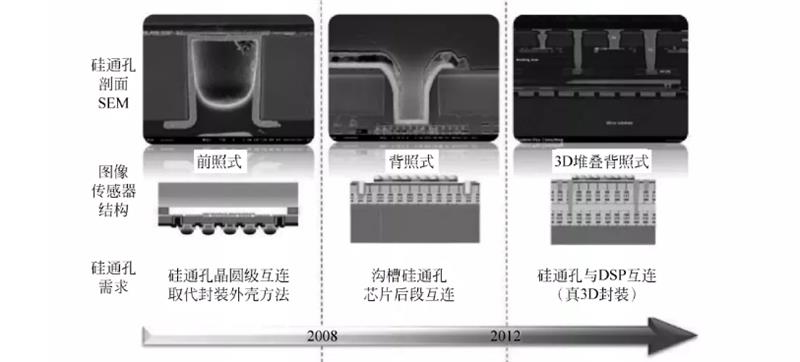

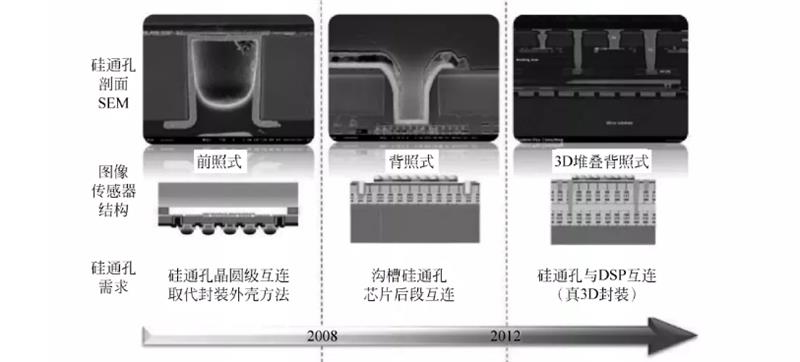

- CMOS 图像传感器:2006 年,东芝公司推出了集成 TSV 技术的产品 ――CMOS 图像传感器 (CIS),并于 2007 年实现量产。性能提升与微型化是推动 CIS 发展的动力。搭载 TSV 的 3D CMOS 图像传感器,其发展历程先后经历了正面成像 (FSI)、背面成像 (BSI),再到混合 3D 堆叠 BSI 的阶段。目前,CIS 是 TSV 技术的应用市场。

- MEMS 领域应用:20 世纪末,深反应离子刻蚀技术开始应用于 MEMS 领域,用于制造多晶硅 TSV (如微悬臂梁、微机械超声换能器阵列所用),以及单晶硅 TSV (如微引擎的二氧化硅沟槽隔离结构)。进入 21 世纪后,多家 MEMS 制造商与代工厂陆续将惯性传感器产品及相关制造服务推向商业化,其中就包含用于晶圆级真空封装 (WLVP) 的气隙隔离式硅 TSV。与此同时,采用空心金属 TSV 与 WLVP 技术的薄膜体声波谐振器 (FBAR) 也实现商业化,广泛应用于无线通信领域。将 TSV 与 WLVP 技术整合到 MEMS 中后,封装尺寸与成本可降至原来的 1/10 到 1/5,这大大加速了近十年来 MEMS 在消费电子与移动电子领域的普及。2014 年,博世公司开发出基于正面中间通孔 TSV 的集成 MEMS 传感器并投入市场,该产品所用 TSV 为 10μm×100μm 的通孔 (深径比 10:1),通过铜电镀制成,相比其他主流 MEMS TSV 集成封装方案,显著缩小了封装的表面积与厚度。目前,MEMS 已成为 TSV 技术的重要应用领域。

- 存储器领域应用:TSV 技术能有效提升存储器的容量与带宽。借助高密度 TSV 垂直互连技术堆叠多个芯片,可显著增强存储器的容量与性能。主流存储器制造商均已采用 TSV 3D 堆叠技术开发相关产品。2009 年,三星公司推出基于 TSV 3D 封装的 8Gb 3D DDR3 DRAM,将待机功耗与工作功耗分别降低 50% 和 25%,并通过 300 个 TSV 将 I/O 速率提升至 1600Mb/s 以上。2014 年,该公司又发布采用 TSV 技术的 16Gb 3D DDR4 SDRAM,其 I/O 速率达到 2.4Gb/s,由 4 个芯片堆叠而成。TSV 技术在高带宽存储器 (HBM) 中也有重要应用。HBM 堆叠并未与 CPU 或 GPU 进行物理集成,而是通过小间距高密度 TSV 转接板实现互连。由于 HBM 具备接近芯片集成 RAM 的特性,因此拥有更快的速度与更高的带宽,适用于对存储器带宽需求较高的场景。在高性能 CPU/GPU 应用中,2.5D TSV 转接板作为平台型技术发挥着关键作用。存储器 (尤其是 HBM 产品) 借助 TSV 技术,带宽得到大幅提升。2014 年,海力士公司发布了采用 29nm 工艺与 TSV 技术的 1.2V 8Gb 8 通道高带宽存储器堆叠 DRAM,带宽达 128GB/s。目前,存储器是 TSV 技术的主要应用市场之一。

- 其他领域应用:功率电子、模拟电子及通信等领域同样是 TSV 技术的重要应用阵地。2021 年,西安理工大学、西安电子科技大学与曼彻斯特大学的 Fengjuan Wang 团队,针对 6G 移动通信需求,提出并研制出基于 TSV 技术的三种五阶超小型发夹式带通滤波器。

关键词:TSV 技术