在高速数据传输领域,PCIe(Peripheral Component Interconnect Express)技术至关重要。本文介绍的是 2019 年 PCI - SIG(PCI Special Interest Group)发布的关于 PCIe 信号设计过程中使用中继器(Redriver&Retimer)的资料,即便在当下,它依然是 PCIe 设计的黄金指南。

目前,许多产品的 PCIe 设计都基于此标准来评估风险。像常见的高速产品服务器,也是依据该标准进行评估的。常见的 PCIe 信号布局形式如下:

图 2 常见 PCIe 信号布局形式

在实际项目评估阶段,会针对不同的拓扑结果进行整理和简单评估。

图 3 项目评估阶段拓扑结果评估

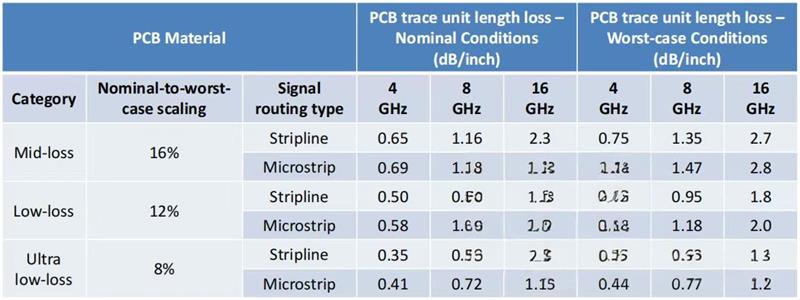

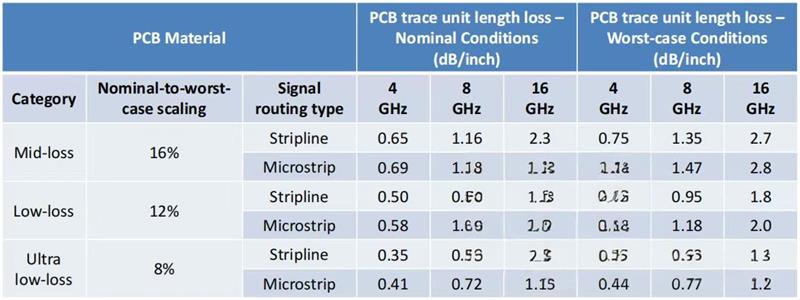

整个链路中,系统端的主板变量,而改善其性能直接的方式就是选择合适的板材。常见的板材分类有 Mid - loss(中损耗)、Low - loss(低损耗)和 Ultra - low - loss(超低损耗)。不过,目前行业对损耗并没有统一的定义和标准,不同板厂以及资料给出的分类也有所不同。

影响插入损耗值的变量因素众多,包括材料特性、布线层、走线宽度、铜箔粗糙度、堆叠结构、环境因素等。设计人员需要根据具体设计和应用场景来确定相应的损耗值。资料还给出了一些不同板材的参考值:

这里需要注意两点:

其一,并非某一分类的所有材料都具有相同性能。有些材料电性能更好,有些材料工艺性能更优,这种取舍需要根据设计产品本身来定位,尤其是在进行产品降本分析时。

其二,除了要注意板厂的制造公差以及不同板厂的制程偏差外,还需特别关注产品的使用环境,如高温高湿等特殊环境会对产品性能产生很大影响,因此在设计产品时需要预留一定的裕量。

如果链路的裕量不足,除了采用升级板材这种较为直接的方式外,还可以考虑使用中继器(Redriver&Retimer)。

输入的模拟信号经过滤波和 / 或放大处理,但抖动和噪声可能恶化或至少维持原状。

内部将模拟信号转换为数据后进行重传输,可实现信号完全再生,但需要付出延迟的代价。

简单来说,Redriver 是 “放大” 信号,而 Retimer 是 “再生” 信号。当主板的信号长度较长、信号损耗严重时,推荐使用 Retimer。

Retimer 器件需邻近扩展槽位置摆放,以确保兼容各类扩展卡 / 线缆(含无源插卡式扩展槽),同时还需综合考量结构件与布线密度因素。

通过运行 IBIS - AMI 仿真验证信号完整性(SI),这里有两点需要关注:

- Retimer 器件的使用包含两个链路段:源端至 RT 段(源端到重定时器)和 RT 至 EP 段(重定时器到终端设备)。

- 各链路段可评估无源信道或 IBIS - AMI(评估含 RC/RT/EP 的完整信道)进行独立仿真。

图 6 Retimer 器件仿真

- 远程环回(Slave Loopback):支持数据从源端(RC)环回到重定时器(RT),或从端点设备(EP)环回到 RT。

- 接收端容限(Receiver Margining):与所有 PCIe 接收器相同,重定时器必须支持通过控制 SKP 有序集(Control SKP Ordered Sets)进行接收端容限测试,可在两个伪端口(BOTH Pseudo Ports)上评估眼图张开度。

- 协议状态(Protocol Status Reporting):重定时器能同时感知上行 / 下行伪端口(Pseudo Ports)的物理层协议事件,可记录此类信息并根据需要上报至系统控制器,助力链路调试,还支持在重大事件(如意外进入 Recovery 状态)时向系统控制器生成中断。

关键词:PCIe 信号