反相器设计详解:原理、类型与性能提升方法

出处:网络 发布于:2025-05-07 15:23:45

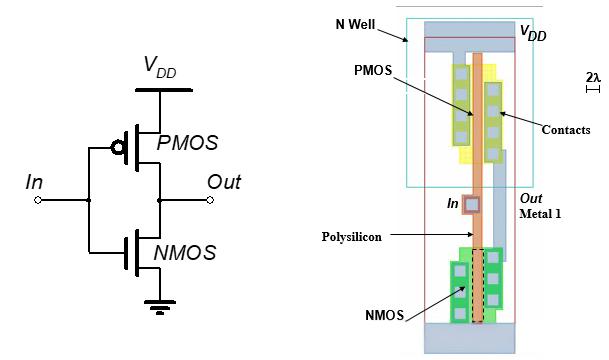

典型的 CMOS 反相器电路由一个 PMOS 晶体管和一个 NMOS 晶体管组成。当输入为低电平时,PMOS 导通,NMOS 截止,输出为高电平;当输入为高电平时,PMOS 截止,NMOS 导通,输出为低电平,从而实现了信号的反相功能。

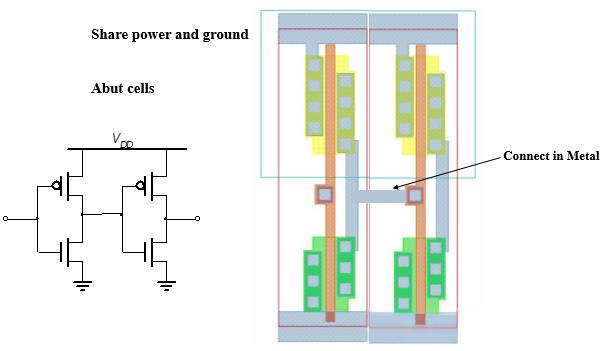

二级 CMOS 反相器是在反相器的基础上进行扩展,通过两个反相器级联,可以进一步增强信号的驱动能力和稳定性。在一些对信号质量要求较高的电路中,二级 CMOS 反相器得到了广泛的应用。

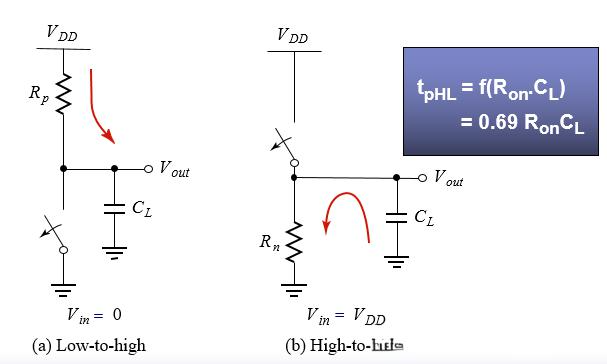

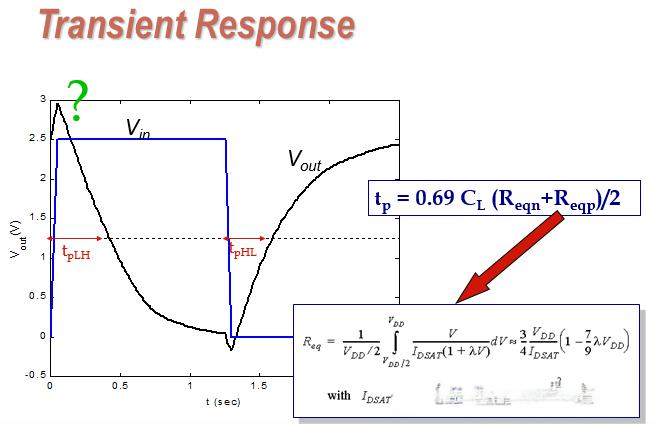

CMOS 反相器在信号传输过程中会存在一定的延时,这主要是由于晶体管的开关特性和电路中的寄生电容等因素引起的。传输延时会影响电路的工作速度和性能,因此需要采取措施来减小延时。

减小负载电容(CL):精细的版图设计有助于减小扩散电容和互连线电容。的设计实践要求漏扩散区的面积越小越好,因为扩散区面积越小,其寄生电容就越小,从而可以减小负载电容对传输延时的影响。此外,合理布局电路布线,减少互连线的长度和交叉,也能有效降低互连线电容。

增加晶体管的宽长比(W/L):这是设计者手中有力和有效的性能优化工具。增加晶体管的宽长比可以提高晶体管的导通电流,从而加快信号的传输速度。然而,增加晶体管的尺寸也会增加扩散电容,这可能会在一定程度上抵消因导通电流增加带来的延时减小效果。因此,在实际设计中需要权衡晶体管尺寸和负载电容之间的关系。

提高电源电压:提高电源电压可以增加晶体管的导通电流,从而减小传输延时。但是,提高电源电压也会带来一些负面影响。首先,会增加能量损耗,这在对功耗要求较高的应用中是一个重要的考虑因素。其次,增加电源电压超过一定程度后,对延时的改善就会非常有限,因而应当避免过度提高电源电压。此外,从可靠性方面考虑,氧化层击穿和热载流子效应等问题迫使在深亚微米工艺中对电源电压要规定严格的上限。

版权与免责声明

凡本网注明“出处:老太阳集团tcy8722网站电子市场网”的所有作品,版权均属于老太阳集团tcy8722网站电子市场网,转载请必须注明老太阳集团tcy8722网站电子市场网,,违反者本网将追究相关法律责任。

本网转载并注明自其它出处的作品,目的在于传递更多信息,并不代表本网赞同其观点或证实其内容的真实性,不承担此类作品侵权行为的直接责任及连带责任。其他媒体、网站或个人从本网转载时,必须保留本网注明的作品出处,并自负版权等法律责任。

如涉及作品内容、版权等问题,请在作品发表之日起一周内与本网联系,否则视为放弃相关权利。

- 电表互感器匝数倍率怎么看?2025/9/5 17:05:11

- 颜色传感器原理及实际应用案例2025/9/5 16:09:23

- 调谐器和调制器的区别2025/9/4 17:25:45

- 有载变压器和无载变压器的区别有哪些2025/9/4 17:13:35

- 什么是晶体谐振器?晶体谐振器的作用2025/9/4 16:57:42